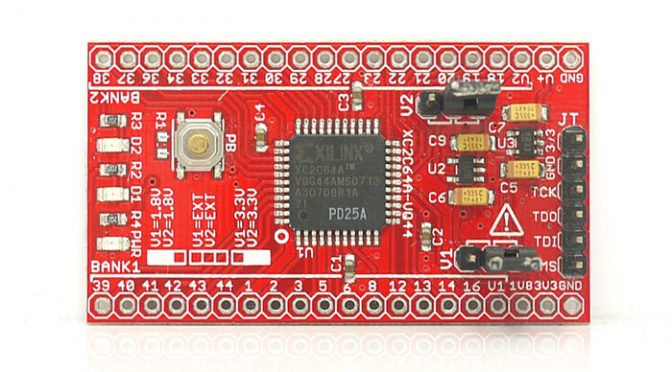

My “go to” tool when breadboarding is often an evaluation board with a Xilinx CPLD. A complex programmable logic device (CPLD) is a programmable logic device with complexity between that of PALs and FPGAs, and architectural features of both.

A CPLD is like a Digikey catalog on a chip. It includes simple logic devices like ANDs, NANDs, ORs, NORs, and XORs. There are Flip-Flops, FIFOs, MUXs, Counters, Compares, Latches, pull ups, pull downs, tri-state I/O, Schmitt triggers, and the list goes on and on. A small device has 64 user I/O ports and larger devices can have 100s of ports.

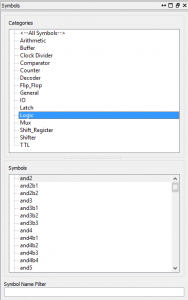

Figure-1 is the pallet of available parts. The Category Logic is selected; the first 13 device showing are ANDs ranging from 2 to 5 inputs. An “and1b1″ is a simple AND with one standard input and 1 inverting input. There are also designs for RS-232/422, SPI, I2C etc on the web that are constructed from the pallet devices.

Once a symbol is placed on the schematic you can right click on the device and see its description and logic table. Most of the time the VHDL code is also available for editing if desired. Knowledge of VHDL or Verilog is not required to design at the schematic level. The schematic symbols are connected by placing a wire or bus between ports.

Ports can be configured into various I/O Standards. A “bank” can be configured for 5.0-volt logic and another bank can be 3.3V, 1.8V or 1.2V which is useful if you need “Glue Logic” between one standard and another.

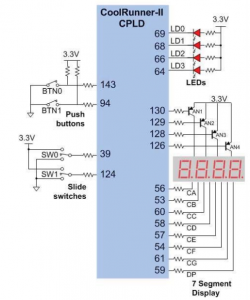

The best part is it is very easy to take advantage of this capability. There are numerous eval-boards priced from $3-$15 for a board like the one in Figure 2.

At the $50 mark, you can get a board with LED lights/digits, buttons, switches, pots, etc.

At higher price points you can get USB, GB Ethernet, HD-LCDs and HMDI ports but they may be beyond schematic level designs and will require VHDL or Verilog skills.

In contrast, there is the dead bug (Figure 2a) approach. The disadvantage to this approach is you must have the “bugs” on hand, the clock rate is limited to a few MHz due to wire length (CPLD clock speed can be > 125MHz), and “edits” are done with a soldering iron with the power off instead of a text editor with the circuit running.

The software tool to configure the CPLD is the Xilinx ISE WebPack which is a free download and a programming dongle that can range from $15 and up. Many boards include the programmer on the board eliminating the need for a dongle, all that is needed is a USB cable to the PC.

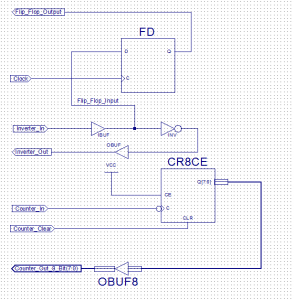

I have designed a small device in Figure-3 as an example. There are 3 distinct circuits. I have included an inverter for those times you have a signal that needs to be inverted, an 8 bit counter with a parallel output, and a Flip-Flop that shares the input with the inverter circuit.

The example shows an Inverter/Flip-Flop circuit and a counter circuit. They are independent of each other. The ability to have a large number of independent parallel circuits gives CPLD/FPGA an advantage over microprocessors in certain applications, especially DSP circuits.

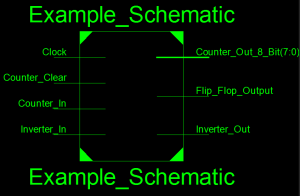

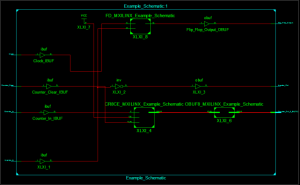

The Xilinx ISE tool will produce a block diagram (Figure-4) of the circuit.

By clicking on the block diagram you can open the detailed circuit (Figure-5), further, the complex elements within the circuit can be expanded.

These are not a “redraw” of the original schematic. They represent the final design after the schematic was translated into HDL by ISE and a circuit design synthesized from the HDL code. This process is transparent to the user. This capability is very useful when designing in HDL. It allows you to discover errors in the code quickly. It is easier for many hardware designers to “debug” the firmware code by following wires on a schematic.

A CPLD board can be very useful in the Ham Shack when positive control is needed. In situations with multiple antenna switches, band switches, and amplifier keyer lines where control logic is important a CPLD design is a great approach. Once the required logic and lockouts are determined the logic design can be completed at the schematic level and the CPLD configured.

The CPLD uses Combinational Logic, it is completely deterministic. Even with a lot of care, a microprocessor has the potential to fall into a disallowed state that could potentially damage equipment. By using hardwired logic this becomes nearly impossible without an actual hardware failure.

If you find an error or change your station simply change the schematic and re-flash the CPLD. (The days of one-use fused link logic are behind us).

Xilinx ISE includes the capability to write a test bench where you describe the full range of inputs and it will display the corresponding output states and timing in Logic Analyzer style. The displayed data is based on actual physical device timing constraints and will allow you to trap switching glitches and logic errors.

While I have focused on CPLDs everything written above can be applied to FPGAs. The different is 100% transparent except the cost may be slightly higher for a small FPGA evaluation board. The first step up from a CPLD in the Xilinx line would be a Spartan device which has considerably most resources and higher performance. While schematic input is an easy place to start ISE is a widely used tool for both VHDL and Verilog HDL coding. It is hoped you would at least dabble in HDL once you have a board.

I have described getting started with CPLDs as easy. I find it much easier than coding in C where just keeping the tool set happy with its countless libraries that must be on the correct path and 100 other ways to generate errors. I enjoy coding in VHDL, for me, it is easier to “think” in terms of wires and buses. With that said there are a few minor hills to get over to start using ISE to configure a CPLD/FPGA.

Here are the three largest issues:

- ISE WebPack is four 2 GB files. An 8 GB total download of compressed .tar files.

- The process of generating and downloading the free license can be a challenge, and then you get to install it.

- Getting an inexpensive aftermarket programming dongle to be recognized by ISE and the PC can require patience.

Once the program is installed and working the rest of the issues are nits. As a hardware designer, I consider them nits.

- You can only attach one wire to a port pin if you want more than one it must be to a buffered pin.

- The logic must be deterministic, in short, you cannot have two outputs tied together unless it is through a AND, OR or similar. Each connection must have a clear “true or false” state.

- The ports you defined in the schematic must be routed to a pin on the CPLD. This is accomplished with a .ucf or User Constraint File. The constraint file format looks like this: NET “name” LOC = “P(pin number)”; That is it.

The following is part of the Constraint file for the schematic shown in Figure 3 and is compatible with the eval-board shown in Figure-2.

| # This is an example of a constraint file | |

| NET "Flip_Flop_Output" | LOC = "P5"; |

| NET "Clock" | LOC = "P30"; |

| NET "Inverter_In" | LOC = "P7"; |

| #NET "P7" | LOC = "P1"; |

| '#' indicates the line is commented out and is ignored | |

Most boards are supplied with a constraint file so you know which pins go to the switches and LEDs, and which ones you can use. If their names are P1, P2, P3 in the constraint file and you have named your ports Clock, Clear, and Count you will hang up on an error. The same is true if you do not use ports P7-P64 in the design and leave them un-commented in the constraint file. If it is in the design it must be in the constraint file, and vice-versa.

- There is a short list of special Key words to include CLK, CLR, and NET. These and other Key words must be avoided until you get past the basics and understand their use.

ISE does a good job of providing a Web link for errors in ISE. The linked page will tell you the problem, likely cause, and the solution.

Here is a schematic of a 4 digit display, it still has 44 user pins available.

If nothing else ISE is a great way to draw schematics.

If you are interested in adding CPLDs and FPGAs to your tool kit I would be more than glad to get you set up and give you a short tutorial.

Hamilton, K1HMS